The computer performs Multiplication in the same way we

perform the operation with pen and paper.

Step 1: Multiplicand

is multiplied by each bit of the multiplier, starting from the least

significant bit.

Step 2: Each

multiplication result forms a partial product. Successive partial products are

shifted one position to the left.

Step 3: The final

product is obtained from the sum of the partial products.

Example:

A

circuit that will implement the multiplication described above in binary is

given in figure 1:

Figure 1: 2-bit x

2-bit binary Multiplier

In practice, there are more bits in the partial products and

it is necessary to use full adders to produce the sum of the partial products.

A combinational circuit binary multiplier with more bits can be constructed in

a similar fashion. For J multiplier bits and K multiplicand

bits, we need (J×K) AND gates and (J-1) K-bit adders to produce a

product of (J+K) bits.

The rest of this short tutorial will illustrate binary

multiplier with a 4×4 bits example, design the circuit, code its implementation

in Verilog HDL and simulate it in ModelSim software.

Let the multiplicand by x3x2x1x0

and the multiplier be y3y2y1y0

With this example our K = 4 and J = 4, we will need (4×4=16)

AND gates and (4-1=3) 4-bits adders, our result will produce a product of

(4×4=16) bits.

: AND gates

: 4-bits binary adders

: Carry bit and the Sum MSB to LSB+1

Figure 2: An algorithm diagram for 4×4 bit

binary Multiplier

Figure 3: Logic Circuit

Diagram of a 4×4 bits binary multiplier

//--------------------------------------------------

//Verilog Code for Binary Multiplier Logic Circuit Design

module binary_multiplier (C, x, y);

input [3:0] x, y;

output [7:0] C;

wire w1, w2, w3, w4, W5, W6, W7, W8;

wire w9, w10, w11, w12, w13, w14, w15,w16;

and (w1, y[0], x[0]);

and (w2, y[1], x[0]);

and (w3, y[2], x[0]);

and (w4, y[3], x[0]);

and (w5, y[0], x[1]);

and (w6, y[1], x[1]);

and (w7, y[2], x[1]);

and (w8, y[3], x[1]);

and (w9, y[0], x[2]);

and (w10, y[1], x[2]);

and (w11, y[2], x[2]);

and (w12, y[3], x[2]);

and (w13, y[0], x[3]);

and (w14, y[1], x[3]);

and (w15, y[2], x[3]);

and (w16, y[3], x[3]);

xor (w0, w1, w1);

wire [3:0] S1, A1, B1;

wire C4_1, C0_1;

wire [3:0] S2, A2, B2;

wire C0_2;

wire [3:0] S3, A3, B3;

wire C0_3;

assign C[0]=w1;

four_bit_adder F_1 (S1, C4_1, A1, B1, C0_1);

four_bit_adder F_2 (S2, C4_2, A2, B2, C0_2);

four_bit_adder F_3 (S3, C4_3, A3, B3, C0_3);

assign A1[0] = w0;

assign A1[1] = w2;

assign A1[2] = w3;

assign A1[3] = w4;

assign B1[0] = w5;

assign B1[1] = w6;

assign B1[2] = w7;

assign B1[3] = w8;

assign C0_1= w0;

assign C[1] = S1[0];

assign A2[0] = S1[1];

assign A2[1] = S1[2];

assign A2[2] = S1[3];

assign A2[3] = C4_1;

assign B2[0] = w9;

assign B2[1] = w10;

assign B2[2] = w11;

assign B2[3] = w12;

assign C0_2= w0;

assign C[2] = S2[0];

assign A3[0] = S2[1];

assign A3[1] = S2[2];

assign A3[2] = S2[3];

assign A3[3] = C4_2;

assign B3[0] = w13;

assign B3[1] = w14;

assign B3[2] = w15;

assign B3[3] = w16;

assign C0_3= w0;

assign C[3] = S3[0];

assign C[4] = S3[1];

assign C[5] = S3[2];

assign C[6] = S3[3];

assign C[7] = C4_3;

endmodule

//-------------------------------------------------

//------------------------------------------------------------------------

// Test bench for Binary Multiplier

module t_binary_multiplier;

wire [7:0] C;

reg [3:0]y, x;

binary_multiplier F1(C, x, y);

initial

begin

x[3:0] =

4'b0000; y = 4'b0000;

#100 x[3:0] = 4'b1010; y = 4'b1001;

#100 x[3:0] = 4'b0010; y = 4'b1001;

end

initial #300 $finish;

endmodule

//--------------------------------------------

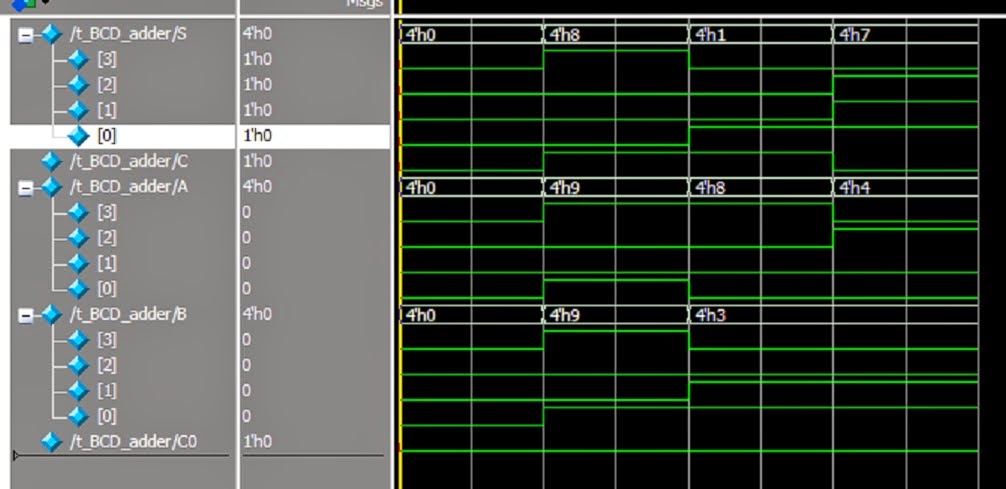

Figure 3: Simulation of binary multiplier in modelSim Showing

initial value of x, y and C.

In figure 3 above,

x = 0000,

y= 0000

C = x×y=00000000 in binary, 0×0 = 0 in decimal.

Figure 4: Figure 3: Simulation of binary multiplier in modelSim

Showing the value of x, y and C at 100ns.

In figure 4;

x = 10102 =10 (decimal),

y

= 10012 =9 (decimal),

C=

x×y = 10×9 = 010110102

= 26+24+23+21

= 64+16+8+2 = 90.

Figure 5: Figure 3: Simulation of binary multiplier in modelSim

Showing the value of x, y and C at 200ns.

In figure 5;

x

= 00102 =2 (decimal),

y

= 10012 =9 (decimal),

C=

x×y = 2×9 = 000100102

= 24+21

= 16+2 =18.